Com o progresso contínuo da tecnologia de semicondutores, o carboneto de silício (SiC), como material de alto desempenho, tem mostrado grande potencial de aplicação na área de dispositivos eletrônicos de potência. No entanto, no processo de preparação do substrato de carboneto de silício, o controle da qualidade da superfície é particularmente crítico, especialmente após desbaste, retificação e polimento e outros processos para obter uma superfície ultralisa. Dentre elas, o polimento químico-mecânico (CMP), como uma das principais etapas, é de grande importância para remover a camada danificada deixada pelo processo anterior e obter alto nivelamento superficial. Porém, o processo CMP tradicional enfrenta o problema da baixa taxa de remoção de material (MRR), o que afeta diretamente a eficiência e o custo da produção. Portanto, explorar novas tecnologias para melhorar a eficiência do CMP do substrato SiC tornou-se o foco da pesquisa atual.

1. Princípios básicos e desafios do substrato SiC CMP

A profundidade do dano superficial do substrato de SiC diluído ou moído é geralmente de 2-5μm e requer tratamento adicional por CMP.

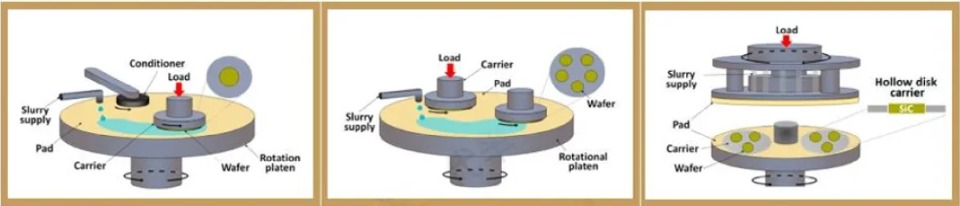

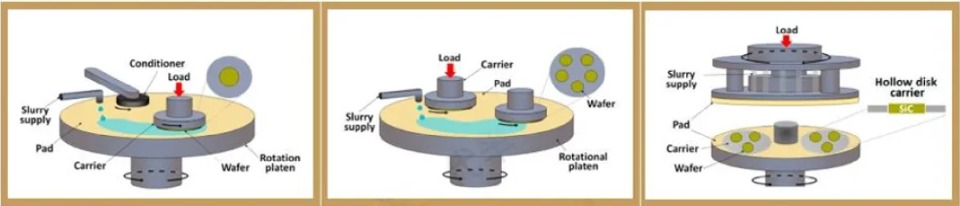

A tecnologia CMP é baseada no princípio composto "químico + mecânico", através da combinação de formação de camada de óxido e remoção mecânica, para obter suavização da superfície.

2. O baixo MRR é o principal problema do substrato de SiC CMP, e a eficiência CMP do SiC é significativamente menor do que a do substrato de silício.

O impacto do baixo MRR na eficiência e nos custos da produção:

MRR mais baixo resulta em etapas CMP de substrato de SiC mais demoradas, aumentando o tempo e o custo de processamento.

Mesmo que o método CMP existente possa produzir substrato 4H-SiC qualificado, a baixa eficiência ainda é o gargalo que restringe sua aplicação em larga escala.

Processo de polimento CMP

3. Progresso técnico para melhorar a eficiência do CMP:

Para enfrentar o desafio do baixo MRR, a indústria desenvolveu tecnologia de polimento em lote frente e verso.

Essas tecnologias avançadas reduziram significativamente as horas de trabalho do CMP, como o tempo de polimento do CMP para um único lote de 10 substratos de 3-5 horas para 1 hora.

A tecnologia de polimento frente e verso não apenas melhora a eficiência, mas também ajuda a manter a consistência e o nivelamento em ambos os lados do substrato.

Em resumo, a melhoria da eficiência do polimento químico-mecânico do substrato de carboneto de silício é a chave para promover sua ampla aplicação. Através do desenvolvimento de tecnologias avançadas, como polimento frente e verso e em lote, o problema da baixa taxa de remoção de material no processo CMP tradicional é efetivamente resolvido, o tempo de processamento é significativamente reduzido e o custo de produção é reduzido. No futuro, com a melhoria contínua dos requisitos de desempenho dos materiais de SiC e a inovação contínua da tecnologia de polimento, temos razões para acreditar que a preparação de substratos de SiC será mais eficiente e económica, estabelecendo uma base sólida para o desenvolvimento futuro de dispositivos eletrônicos de potência. Portanto, a exploração e otimização contínua do processo CMP será uma forma importante de promover a ampla aplicação de materiais SiC no campo de semicondutores.